IBM 宣布推進 2nm 製程晶片試產,目標讓量子運算、人工智慧等技術加速成長

【此文章來自:Mashdigi】

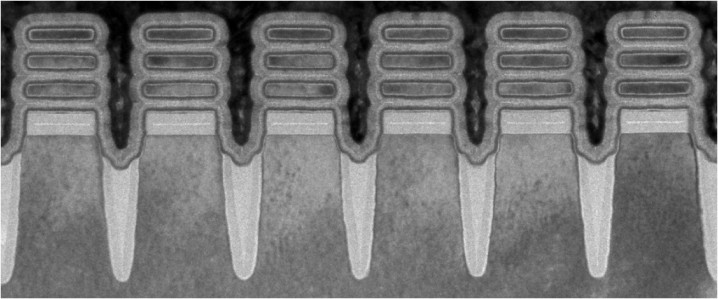

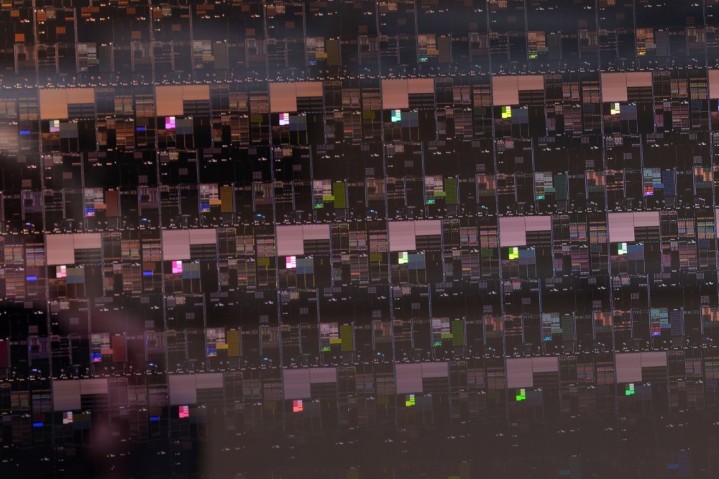

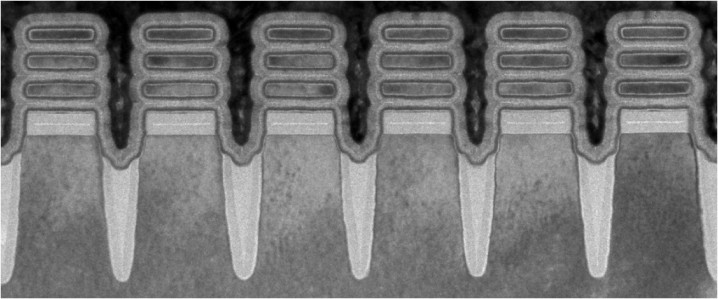

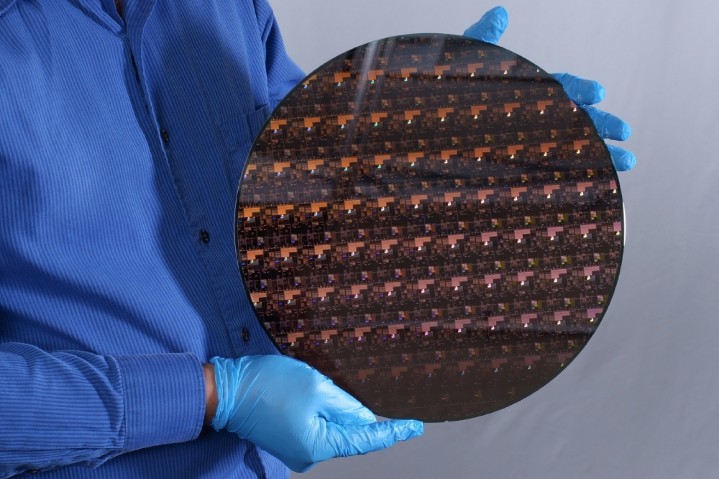

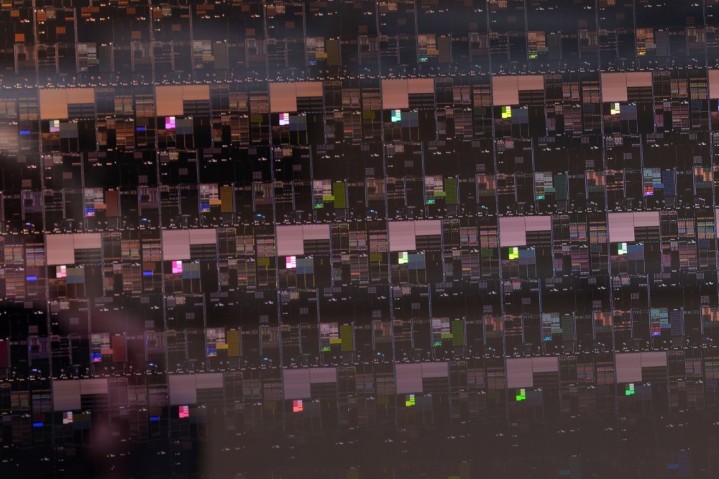

相較台積電採用的 FinFET 製程技術,或是三星採用光照技術,IBM 採用以 GAA 環繞式結構設計的 Nanosheet 奈米片技術,每組電晶體均透過三層水平堆疊奈米等級矽片構成,約可在 150 平方公厘 (mm²) 面積晶圓中放置 500 億組電晶體,亦即在每平方公厘可放置 3.3 億組電晶體。

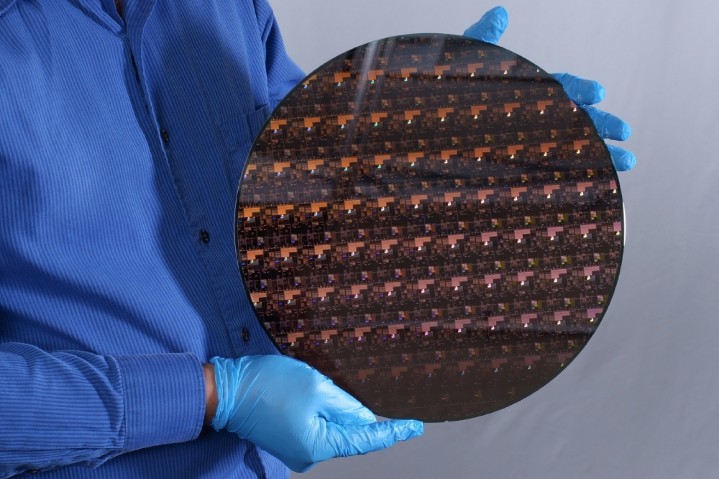

目前 IBM 是由位於紐約州奧爾巴尼的晶片製造研發中心進行試產,並且與三星、Intel 簽署共同技術開發協議,因此三星、Intel 可藉由 IBM 開發技術製造晶片產品。

依照說明,相比 7nm 製程的運算效能,2nm 製程晶片在相同電力表現可提升 45% 運算效能,而在相同效能表現之下,2nm 製程晶片更可減少高達 75% 電力損耗,意味應用在手機晶片上的話,將可讓目前使用的智慧型手機對應 4 天左右的電力使用時間,同時也讓更多運算裝置不必擔心電力損耗問題。

製程技術持續推進,IBM 認為將能讓運算規模有大幅成長,其中包含量子運算領域應用,或是包含人工智慧、自動駕駛,或是目前在 5G 網路應用技術,甚至日後的 6G 網路發展。

而雖然目前宣布推進 2nm 製程,但畢竟仍處於試產階段,距離可大量生產可能還需要一點時間,IBM 目前並未特別說明預計進入量產時程。

相比 7nm 製程,在相同效能表現則可節省高達 75% 電力損耗

IBM 稍早宣布已經順利試產其下首款 2nm 製程晶片,並且標榜在相同電力情況下,2nm 製程晶片將比 7nm 製程產品提升 45% 運算效能,在相同效能表現則可節省高達 75% 電力損耗。

相較台積電採用的 FinFET 製程技術,或是三星採用光照技術,IBM 採用以 GAA 環繞式結構設計的 Nanosheet 奈米片技術,每組電晶體均透過三層水平堆疊奈米等級矽片構成,約可在 150 平方公厘 (mm²) 面積晶圓中放置 500 億組電晶體,亦即在每平方公厘可放置 3.3 億組電晶體。

目前 IBM 是由位於紐約州奧爾巴尼的晶片製造研發中心進行試產,並且與三星、Intel 簽署共同技術開發協議,因此三星、Intel 可藉由 IBM 開發技術製造晶片產品。

依照說明,相比 7nm 製程的運算效能,2nm 製程晶片在相同電力表現可提升 45% 運算效能,而在相同效能表現之下,2nm 製程晶片更可減少高達 75% 電力損耗,意味應用在手機晶片上的話,將可讓目前使用的智慧型手機對應 4 天左右的電力使用時間,同時也讓更多運算裝置不必擔心電力損耗問題。

製程技術持續推進,IBM 認為將能讓運算規模有大幅成長,其中包含量子運算領域應用,或是包含人工智慧、自動駕駛,或是目前在 5G 網路應用技術,甚至日後的 6G 網路發展。

而雖然目前宣布推進 2nm 製程,但畢竟仍處於試產階段,距離可大量生產可能還需要一點時間,IBM 目前並未特別說明預計進入量產時程。

廣告

Mashdigi

出生自台灣高雄的楊又肇,以前聯合新聞網 (udn.com)數位頻道主編,以及在各網站頻道以本名或Mash Yang名稱維持提供撰寫、授權內容等身分,持續在網路、科技相關活動、展覽出沒。撰寫內容涵蓋個人感興趣內容,包含手機、網路、軟體、零組件,以及科技市場動態,另外也包含各類惡趣味內容,並且持續關注蘋果、微軟、Google、Intel、AMD、Nvidia等經常在你我生活中出現的科技廠商動態。

網友評論 0 回覆本文