三星公布自有 3D 立體堆疊封裝技術 X-Cube

【此文章來自:Mashdigi】

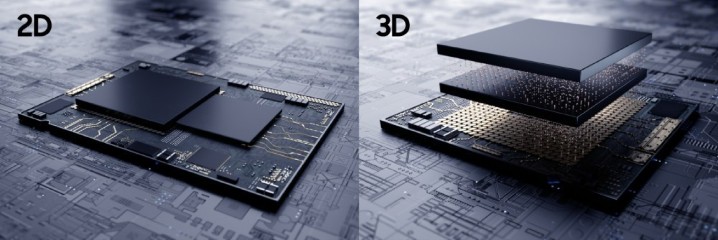

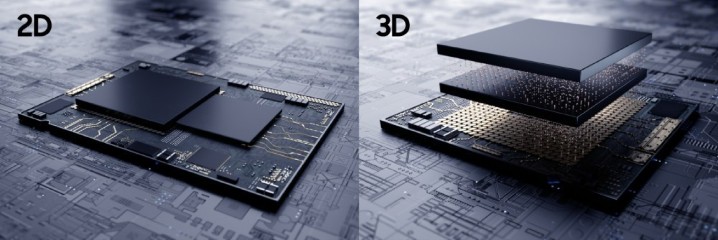

X-Cube 名稱源自「eXtended-Cube」之意,將原本以 2D 平面封裝形式改為 3D 堆疊,讓處理器能在有限面積內容納更多電晶體,同時也能讓處理器以更少電力即可驅動。三星先前已經透過 X-Cube 封裝技術將 SRAM 層堆疊在運算邏輯層上,並且透過 TSV 矽穿孔設計進行串接,其中更以自家 7nm EUV 製程技術打造。

三星表示,X-Cube 封裝技術將使處理器內部 Die 之間的訊號傳遞距離縮減,藉此加快數據運算效率,並且讓整體電力損耗連帶降低,更強調此項封裝技術將能應用在高效能運算處理器、5G 連網數據晶片,或是人工智慧運算晶片。

而目前 X-Cube 封裝技術已經在三星旗下 7nm 與 5nm 製程技術進行驗證,並且準備應用在旗下處理器產品,或是協助其他處理器設計廠商生產產品。

除了三星,目前包含台積電旗下 CoWoS 封裝技術,以及 Intel 提出的 Foveros 封裝技術,都是藉由 3D 堆疊概念讓處理器內部空間能放置更多電晶體數量,藉此發會更高運算效能。

預計用在高效能處理器、5G 數據晶片與人工智慧運算元件

三星稍早宣布推出自有 3D 立體堆疊封裝技術,並且確定以 X-Cube 為稱,預期藉此縮減旗下處理器面積尺寸,將更有利於讓處理器可應用在更小裝置內。

X-Cube 名稱源自「eXtended-Cube」之意,將原本以 2D 平面封裝形式改為 3D 堆疊,讓處理器能在有限面積內容納更多電晶體,同時也能讓處理器以更少電力即可驅動。三星先前已經透過 X-Cube 封裝技術將 SRAM 層堆疊在運算邏輯層上,並且透過 TSV 矽穿孔設計進行串接,其中更以自家 7nm EUV 製程技術打造。

三星表示,X-Cube 封裝技術將使處理器內部 Die 之間的訊號傳遞距離縮減,藉此加快數據運算效率,並且讓整體電力損耗連帶降低,更強調此項封裝技術將能應用在高效能運算處理器、5G 連網數據晶片,或是人工智慧運算晶片。

而目前 X-Cube 封裝技術已經在三星旗下 7nm 與 5nm 製程技術進行驗證,並且準備應用在旗下處理器產品,或是協助其他處理器設計廠商生產產品。

除了三星,目前包含台積電旗下 CoWoS 封裝技術,以及 Intel 提出的 Foveros 封裝技術,都是藉由 3D 堆疊概念讓處理器內部空間能放置更多電晶體數量,藉此發會更高運算效能。

廣告

網友評論 0 回覆本文