台積電 3nm 製程技術超前,預計 2022 年進入正式量產階段

【此文章來自:Mashdigi】

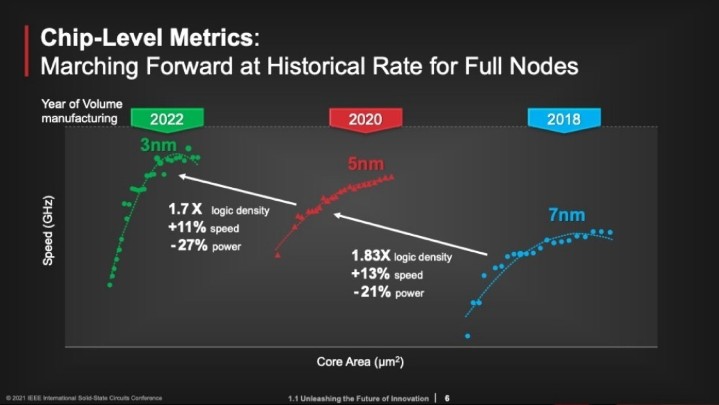

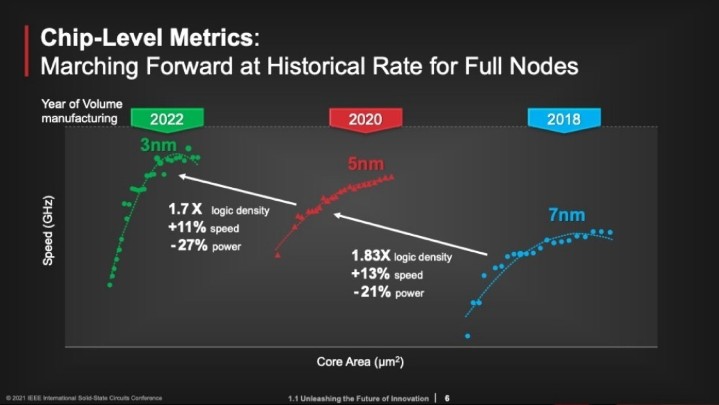

相較目前進入量產的 5nm 製程,台積電表示在 3nm 製程技術將可讓電晶體密度提高 70%,並且讓晶片運作時脈可達生 11%,或是讓電功耗降低 27%。

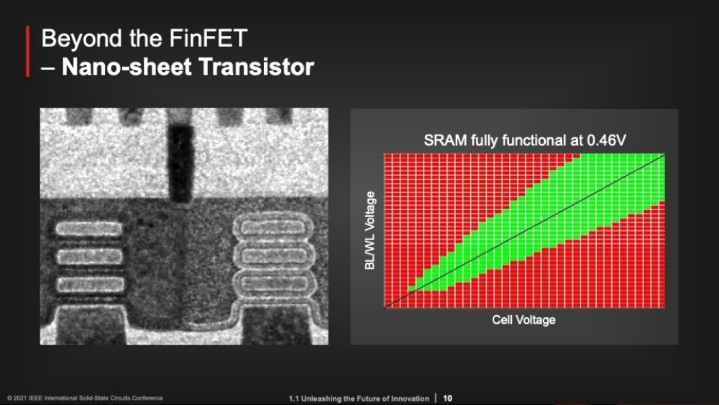

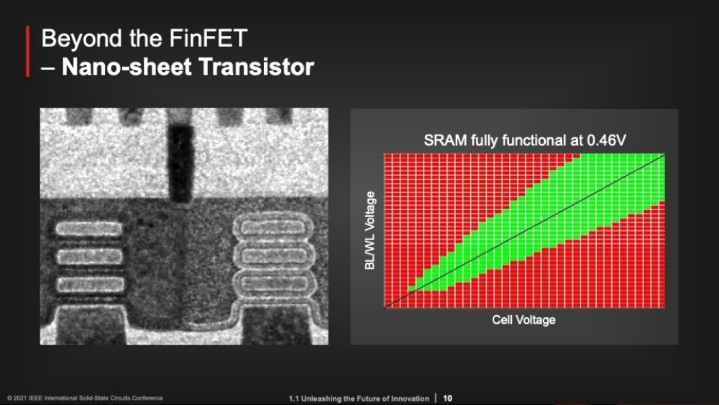

不過,跟三星在 3nm 製程技術導入環繞式閘極結構 (GAA) 電晶體的作法不同,台積電在第一代 3nm 製程技術依然維持採用鰭式場效 (FinFET) 電晶體設計,但未來同樣也會在 EUV 光刻技術應用著力,不僅能藉由 350W 功率對應 5nm 製程技術使用,未來也能用於 1nm 製程技術。

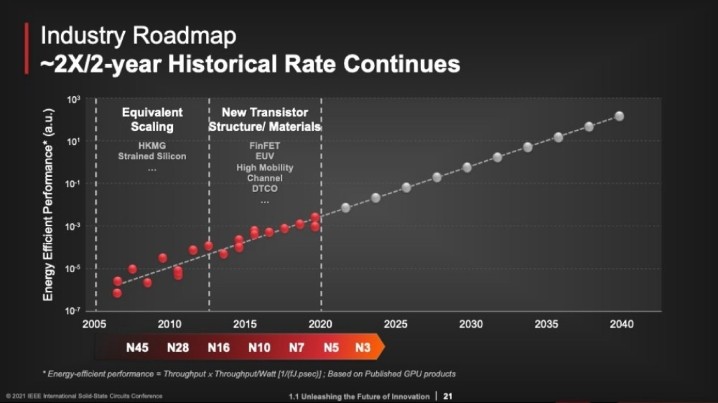

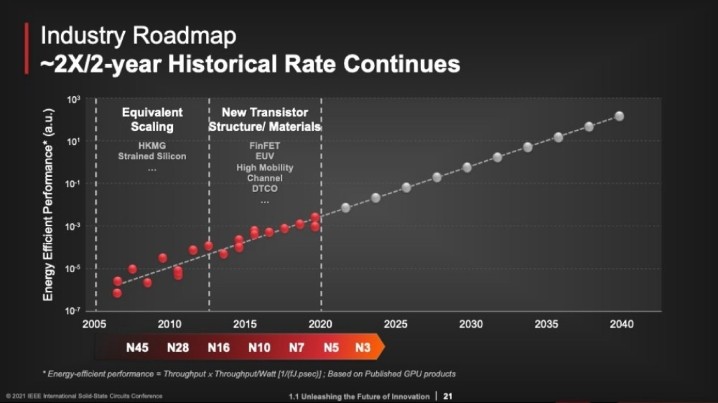

依照劉德音表示,預期未來的半導體產業依然會延續摩爾定律成長,包含每 2 年升級一次製程技術,同時每隔 10 年就會有一次重大技術改革。

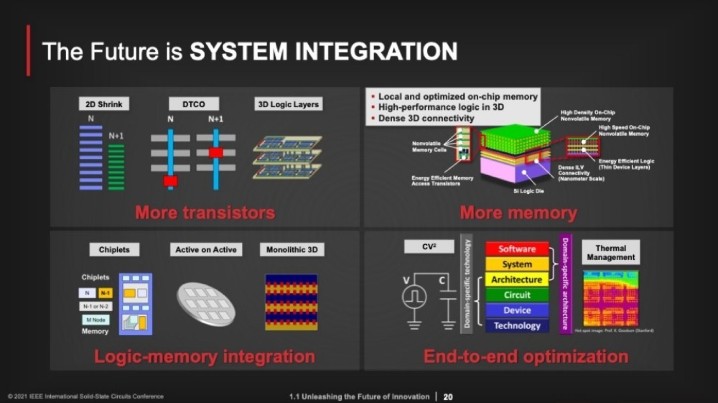

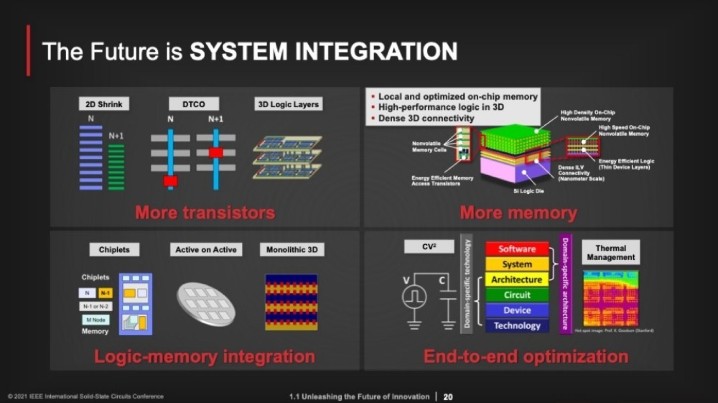

此外,隨著製程技術持續縮減,未來晶片設計將會結合更多員堆疊應用模式,例如導入更多電晶體數量、嵌入更多記憶體模組,或是強化系統單晶片形式設計。

強調未來也會強化 EUV 光刻應用

台積電在近期展開的國際固態電路研討會 ISSCC 2021 中,由董事長劉德音表示 3nm 製程技術進度超前,預計會在今年下半年進入試產,並且在 2022 年正式用於量產。

相較目前進入量產的 5nm 製程,台積電表示在 3nm 製程技術將可讓電晶體密度提高 70%,並且讓晶片運作時脈可達生 11%,或是讓電功耗降低 27%。

不過,跟三星在 3nm 製程技術導入環繞式閘極結構 (GAA) 電晶體的作法不同,台積電在第一代 3nm 製程技術依然維持採用鰭式場效 (FinFET) 電晶體設計,但未來同樣也會在 EUV 光刻技術應用著力,不僅能藉由 350W 功率對應 5nm 製程技術使用,未來也能用於 1nm 製程技術。

依照劉德音表示,預期未來的半導體產業依然會延續摩爾定律成長,包含每 2 年升級一次製程技術,同時每隔 10 年就會有一次重大技術改革。

此外,隨著製程技術持續縮減,未來晶片設計將會結合更多員堆疊應用模式,例如導入更多電晶體數量、嵌入更多記憶體模組,或是強化系統單晶片形式設計。

廣告

網友評論 0 回覆本文